#### SysAdmin Group Presentation

# Field-Programmable Gate Array Development

Igor Senderovich

April 17, 2008

#### Outline

- 1. Introduction: Computer-Aided Hardware Design

- 2. FPGA Design Flow

- 3. General hardware programming issues

- i. Hardware programming *state of mind*

- ii. Hardware Description Languages

- iii. Component Specification

- 4. VHDL

- i. Example 1: Basic Logic and Synchronization

- ii. Example 2: 3-bit register

- 5. Implementation

- 6. Deployment

## **Computer-Aided Hardware Design**

- The key phrase is Computer-Aided

- Computer provides:

- Design aids: programming environment, visualization etc.

- Simulation environment: functionality and performance prediction

- Computer does NOT provide a <u>native</u> test environment

- Software Hardware Comparison to software Coding Coding development: Synthesis ? Compilation **Behavioral Model** (Interpretation) Implementation Device Programming Native Testing **In-Circuit Testing**

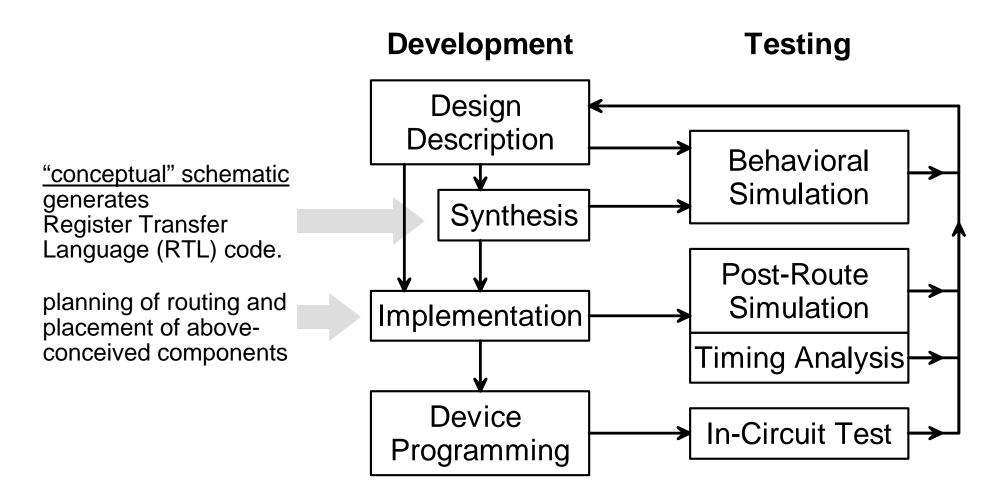

#### More Detailed FPGA Design Flow:

- No expectations of sequential processing!

- All components are "on" and responding to stimulus; all parts of the code are working at once.

- Order restored with Chip Enable (CE) pins, gates, component's internal counters: quiet until a "Go" signal

- Scope:

- Component's signals: internal or patched outside for sharing

- Shared signal access: "whoever cares to connect" → constant state of "sharing violation". Solutions:

- Separate communication lines

- Components writing to same line are enabled one at a time. Pins of quiet components set to high impedance.

#### • HDL – Hardware Description Language (generic term)

- Verilog designed to resemble C

- VHDL language based on Ada

- 'V' for VHSIC (Very-High-Speed Integrated Circuits)

- product of a 1980s U.S. Defense project

- Other, less common languages

- **ABEL** (Adv. Boolean Expression Lang.)

- **AHDL** (Altera's proprietary language)

- Atom, Bluespec, Hydra, Lava (Haskell-based)

- **CUPL** (proprietary: Logical Devices, Inc.)

- HDCaml (based on Objective Caml)

- Hardware Join Java

- HML (based on SML)

- JHDL (based on Java)

- Lola (a pedagogical tool)

- **MyHDL** (based on Python)

- **PALASM** (for Prog. Array Logic (PAL) devices)

- **Ruby** (hardware description language)

- **RHDL** (based on the Ruby prog. language)

- SystemVerilog (superset of Verilog+)

- **SystemC** (C++ libraries for system-level modeling)

## **Component Specification**

- Instantiation Components added from libraries much like functions from API dynamic libraries.

- Offers full control of the use of components

- Useful (and sometimes only allowed) for complicated parts with standard, well-circumscribed behavior

- Works well with visual schematic design/programming

- **Inference** Components are *inferred* from functionality described in the programming.

- Readable/portable code

- The only approach to simple components (likely majority of design)

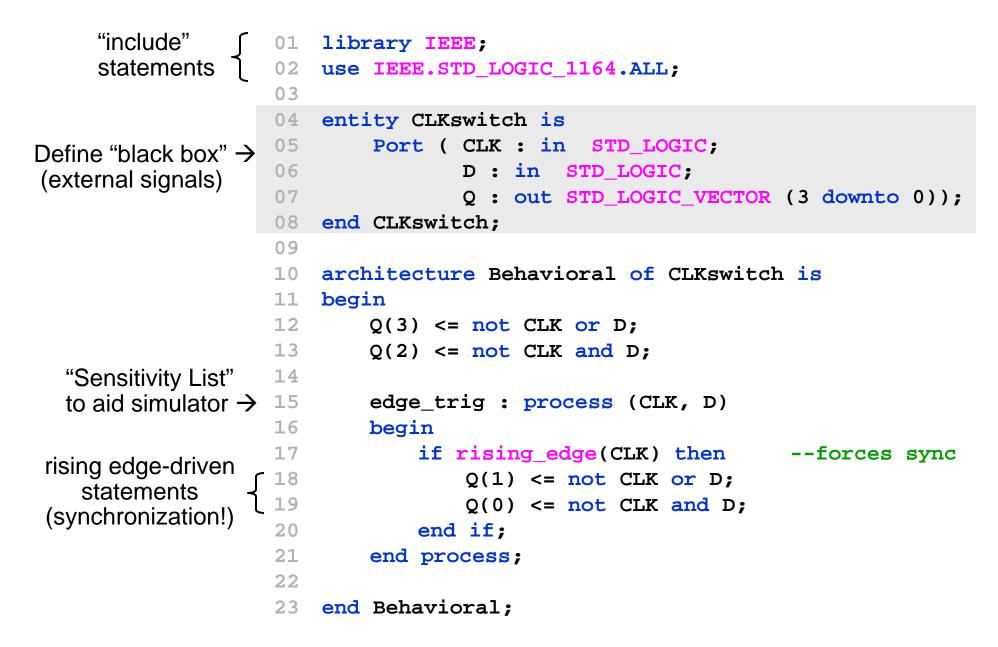

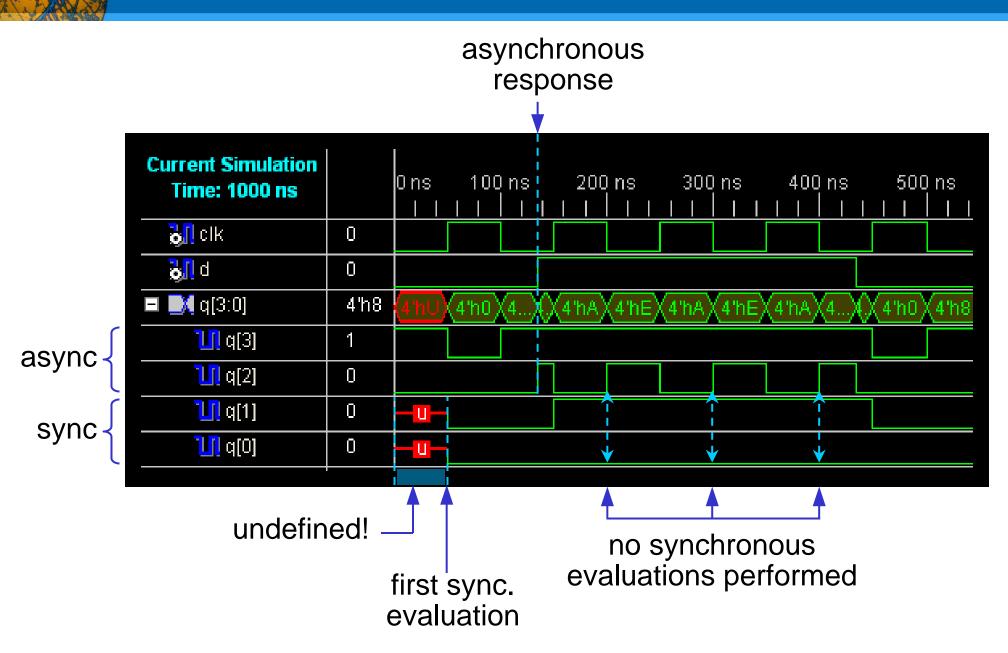

## Ex. 1: Basic Logic and Synchronization

Igor Senderovich, "Field-Programmable Gate Array Development"

## Ex. 1: Basic Logic and Synchronization

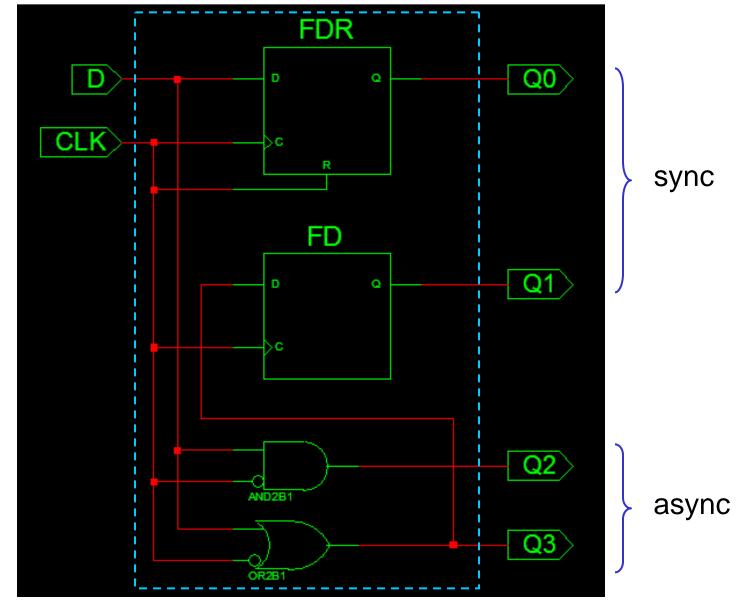

**RTL Schematic:**

April 17, 2008

Igor Senderovich, "Field-Programmable Gate Array Development"

## Ex. 1: Basic Logic and Synchronization

#### Ex. 2: 3-bit Register

20

| Internal                              | 01 |

|---------------------------------------|----|

| signal declared $ ightarrow$          | 02 |

|                                       | 03 |

| "Sensitivity List"                    | 04 |

| to aid simulator $\rightarrow$        | 05 |

|                                       | 06 |

| Reset to avoid                        | 07 |

| undefined behavior $\rightarrow$      | 08 |

|                                       | 09 |

|                                       | 10 |

|                                       | 11 |

| Explicit request                      | 12 |

| for storage $\rightarrow$             | 13 |

| (often inferred anyway)               | 14 |

| · · · · · · · · · · · · · · · · · · · | 15 |

|                                       | 16 |

|                                       | 17 |

|                                       | 18 |

|                                       | 19 |

```

architecture Behavioral of stateReg is

signal state : STD LOGIC VECTOR (2 downto 0);

begin

LatchInput : process (Clk, Rst, En)

begin

if (Rst = '1') then

state <= "000";</pre>

else

if (falling_edge(Clk) and En='1') then

state <= D;</pre>

else

state <= state;</pre>

end if;

end if;

end process LatchInput;

Q <= state;

end Behavioral;

```

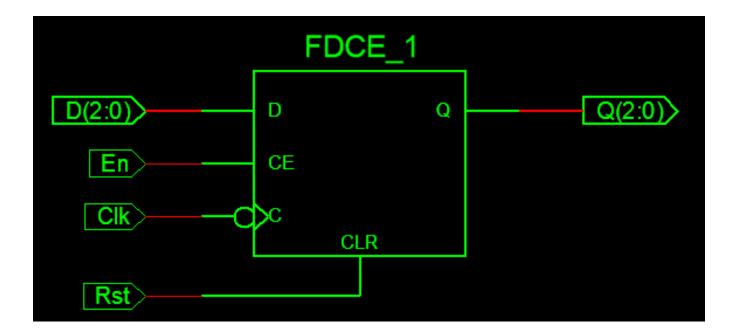

#### Ex. 2: 3-bit Register

#### A Standard Register Component!

## Ex. 2: 3-bit Register

| Current Simulation<br>Time: 10000 ns |      | 0 ns 500 ns 1000 ns 1500 ns 2000 ns 2500 ns 3000 ns<br>             |

|--------------------------------------|------|---------------------------------------------------------------------|

| <mark>ð II</mark> elk                | 1    |                                                                     |

| <mark>₀,∏</mark> rst                 | 0    |                                                                     |

| 🌏 👖 en                               | 0    |                                                                     |

| 🗖 🛃 d[2:0]                           | 3'h0 | <u>3'n0 \3'n3 3'n0 \3'n3\3'n0\3'n1\3'n0\3'n1\ 3'n0 \3'n1\3'n2 \</u> |

| <mark>ð</mark> [] d[2]               | 0    |                                                                     |

| <mark>ð</mark> [] d[1]               | 0    |                                                                     |

| <mark>ð</mark> ,[] d[0]              | 0    |                                                                     |

| 🗖 🛃 q[2:0]                           | 3'h0 | <u>3"hU 3"h0 X 3"h3 X 3"h0 X3"h1 3"h2 X</u>                         |

| <b>ð,[]</b> q[2]                     | 0    |                                                                     |

| <mark>ढे, </mark> q[1]               | 0    |                                                                     |

| <mark>ढु,]]</mark> q[0]              | 0    |                                                                     |

|                                      |      |                                                                     |

|                                      |      | latched on falling ignored register clock edge                      |

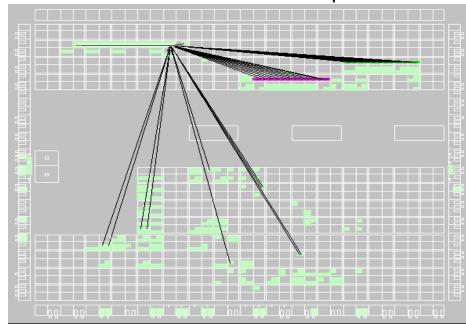

#### Implementation

- A more concrete plan of components, their placement and routing in the Gate Array is generated

- Constraint and optimization details specified

- Auto-generated maps adjusted

- Timing and power consumption analyzed

- More realistic simulations

- Functionality verified

- Timing tested

Sample Floor Plan

## **FPGA Configuration Schemes**

- FPGA is fed a programming bit stream. Sources:

- In-System: using computer interface: useful in the prototyping stage

- In the Field (after deployment): E<sup>n</sup>PROM, n = 0,1,2 on-board and activated on power cycle\*

- More custom solutions possible (e.g. microcontroller or CPLD-directed programming on startup)

\* Non-volatile FPGA's are available, eliminating the need for programming sources after the development stage